Adaptive Hardwarebeschleuniger auf Basis partiell dynamisch rekonfigurierbarer FPGAs

Hardware-Acceleration of Semantic Web Databases via dynamic reconfigurable FPGAs

In the Semantic Web, dependencies are generated via triples of subjects, predicates, and objects. Due to enormous data sizes special data structures are developed, which enable parallelized and efficient access. As part of this project, the generation and query processing on such database systems realized on hardware accelerators is researched.

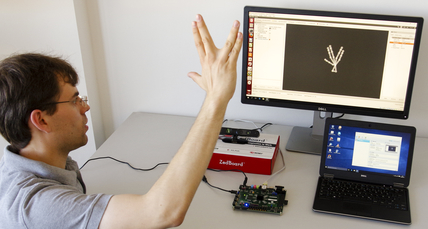

Hardware-Accelerated Pose Estimation for Embedded Systems

The focus of this projects is to facilitate pose estimation and, thus, gesture recognition for embedded systems, although these are tasks with high computational performance requirements. Therefore, an existing pose estimation algorithm is optimized for Xilinx High Level Synthesis (HLS). The resulting hardware acceleration cores are compared for different optimizations and, finally, we propose a hardware/software system design for a Xilinx Zynq Zedboard. Using this method, we achieve a speedup in comparison to a software solution on the ARM processor and, thus, facilitate hand tracking for embedded systems with low power consumption in real time.